뉴로모픽 기술과 멤리스터

전기·전자 분야의 기술은 1971년 인텔의 4비트 CPU의 개발로부터 시작되었다고 해도 과언이 아니다.

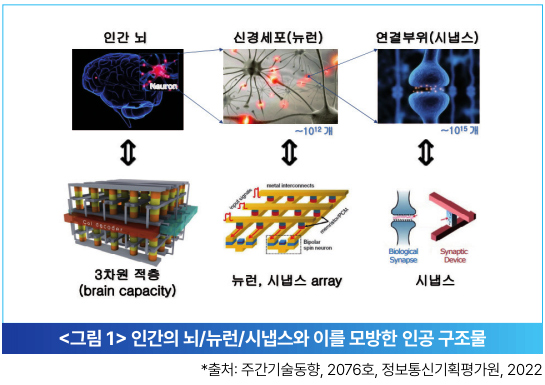

무어의 법칙에 따라서 급속하게 발전하기 시작한 반도체 기반의 컴퓨팅 기술은 최근 들어 인공지능 기술과 융합되면서 또 다른 변곡점을 맞고 있다. 얼마 전 인공지능 바둑 프로그램인 알파고의 놀라운 성능은 AI의 새로운 패러다임을 활짝 열었다. 이 알파고의 경우 연산을 위해서는 1,000개 이상의 CPU와 병렬처리를 위한 200여 개의 그래픽 카드 및 100만 개 이상의 메모리가 필요하였다. 앞으로 보다 복잡한 연상을 위한 방대한 데이터의 처리에는 더 많은 CPU, 그래픽 카드 및 메모리가 필요하며 이들 소자의 운용을 위해서는 엄청난 전력이 소요되는 것은 불문가지다. 그러므로 현재의 문제를 극복하기 위해서는 폰 노이만 방식의 소자가 아닌 새로운 개념의 소자의 출현이 요청되고 있다. 단순한 0과 1의 반복적 연산이 아니라 인간의 두뇌의 원리를 모사함으로써 저전력으로 높은 연산 수행도를 나타낼 수 있는 소자는 폰 노이만 구조의 소자가 갖는 단점을 보완하기에 충분할 것으로 기대되고 있다. <그림 1>은 인간의 두뇌를 모사한 전자소자의 개념을 나타냈다.

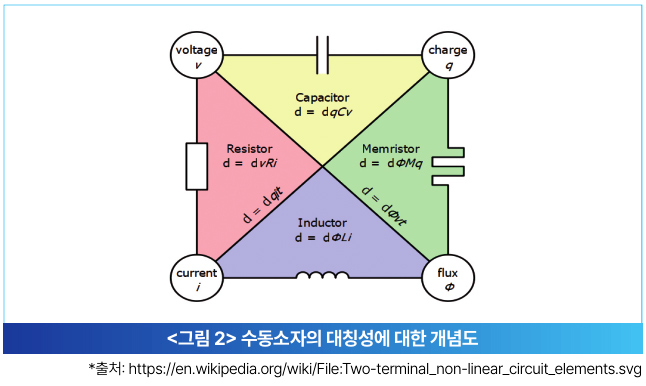

이러한 시대적 상황을 배경으로 멤리스터 소자가 탄생하였다. 전기회로를 구성하는 수동소자는 저항, 인덕터, 캐패시턴스 등 세 종류로 나눌 수 있다. 그러나 1971년 Leon Chua는 4개의 소자가 이루는 대칭 성에 기반한 소자의 개념을 도입하였다. 기존의 수동소자들은 전류와 전압과의 관계를 규정하는 저항, 전압과 전하량과의 관계를 규정하는 캐패시터, 그리고 전류와 자속관계를 정의하는 인덕터이다. 그런데 이때 전하 (charge)와 자속(magnetic flux)과의 관계를 정의하는 소자가 없기 때문에 대칭이 무너져 있다고 주장하였다. 따라서 이러한 대칭성을 완성하기 위하여 Leon Chua는 멤리스터라는 소자를 도입 하였다. <그림 2>는 4개의 수동소자의 정의를 대칭적 그림으로 나타낸 것이다.

그러나 개념적으로 도입된 멤리스터 소자는 기존의 소자에 비해 구체적 실체를 이해하기에 어려움이 있었다. 그래서 멤리스터 소자의 제안자인 Chua는 아래의 특성을 갖는 소자를 멤리스터로 정의할 수있다고 가이드를 제시하였다. 첫째는 어떠한 조건을 초기에 인가하였다 하더라도 +/- 극에 상관 없이 주기적인 전압 또는 전류로 구동되며, 이때 전압-전류 그래프에서 좁은 히스테리시스 곡선을 형성할 경우 멤리스터 소자로 판정할 수 있다는 것이다. 둘째, 이때 형성된 히스테리시스 루프의 내부 면적이 인가한 신호의 주파수 증가에 따라 반비례하여 수축하여야 한다. 마지막으로는 주파수가 무한대가 될경우 히스테리시스 곡선은 점차로 원점을 지나는 직선으로 변화하는데, 이때 이 직선의 기울기가 인가한 신호의 진폭 및 형상에 따라 바뀌는 동작할 경우 측정된 소자는 멤리스터 소자로 규정지을 수 있다고, 세가지 필요충분조건을 제시하였다.

그러므로 최근 들어 기존의 메모리 소자와 다른 특성을 지니고 있다고 판단되는 ReRAM, MRAM (Magnetic Random Access Memory), PCM (Phase Change Memory) 등과 같은 비선형 소자의 경우는 Chua의 기준에 따르면 멤리스터 소자의 범주에 속하는 것으로 판단할 수 있다. 멤리스터는 전기소자에서 발생하는 자속과 전하 사이의 관계를 규정하는 소자로서 Chua는 2011년에 발표한 논문인 ‘Resistance switching memories are memristors’에서 멤리스터 소자의 저항은 일반적인 저항기와 달리 이 소자를 통과하였던 이전 전류의 과거 정보에 의존적이라는 것을 도입하였다. 따라서 멤리스터 소자는 전력이 단락된 후 다시 가동 시 최종 제공된 전력 공급 시 저항 상황으로 복귀하는 특성을 갖게 된다는 것으로 해석할 수 있다. 1)

를 기반으로 하는 나노 두께 및 크기를 갖는 박막형 멤리스터 소자를 제작하여 이론만으로 존재하던 멤리스터 소자의 거동을 제작한 소자를 통하여 실증하는 데 성공하였다. 당시 제작한 실제 소자의 경우 자속과 전하의 관계성을 완벽하게 입증하지 못했지만, 전류 이력에 대한 의존성을 충실히 보여주어 멤리스터의 필요충분조건을 만족하고 있음을 보여 주었다. 이 연구 이후 ReRAM, MRAM, PCM 등의 소자와 함께 멤리스터 소자의 연구가 활발히 진행되고 있으며, 인공지능을 구현하기 위한 뉴로모픽 소자의 필요성이 높아지며 연구 영역이 확대되고 있다.

1) Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, S. R. (2008), “The missing memristor found”, Nature, 453 (7191), pp. 80–83.

기술개발의 중요성

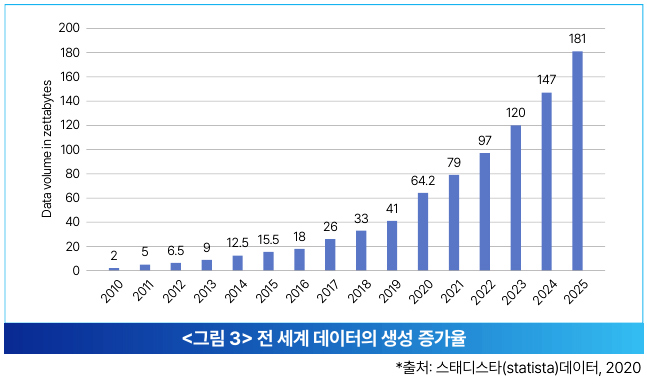

다양한 인공지능 서비스가 속속 등장하면서 이를 뒷받침할 수 있는 새로운 소자들에 대한 요구도 급증 하고 있다. 특히 인간의 뇌를 모사하여 작동할 수 있는 새로운 구조의 뉴로모픽 소자(Neuromorphic devices)의 개발도 더욱 가속화되고 있다. 급증하는 데이터 처리량과 고속처리속도에 대한 소비자들의 요청에 대응하기 위한 에너지의 요구량은 기하급수적으로 증가하고 있다. 관련 데이터센터의 전력 소모 량은 2020년 기준으로 약 2조 kWh에 달하고 있으며, 더욱 가파르게 늘어날 것으로 예측된다. 데이터 처리량이 시간에 따라 증가하는 양상을 보이는 것을 <그림 3>에서 확인할 수 있다.

한편, 인간의 뇌를 모사하여 개발하고 있는 인공지능 소자의 경우 인체와 유사성을 갖추기 위해서는 인간의 뉴런 수인 1,000억과 100조 개의 시냅스를 모방해야 한다고 알려져 있다. 이를 구현하기 위해서 현재의 기술은 6~8개의 SRAM(Static Random Access Memory)을 이용하여 뉴런을 모방하고 있다. 그러므로 이렇게 구성된 뉴런 모방소자를 구동하기 위해서는 기존 소자보다 더 많은 전력이 요구되며, 시냅스의 증가에 따라 요구 전력은 기하급수적으로 증가하게 된다. 따라서 소비 전력을 획기적으로 저감시킬 수 있는 소자인 멤리스터의 적용은 저전력으로 효율성 높은 뉴로모픽 시스템을 구축할 수 있는 지름길이 될 것으로 예측된다.

뉴로모픽 기술에 기반한 인공지능 기술은 4차 산업혁명 이후의 새로운 혁명을 이끌 수 있는 새로운 패러 다임을 제시할 수 있는 기술로 등장하고 있다. 또한 기존의 컴퓨팅 기술인 폰 노이만 방식의 연산 방법을 넘어서는 새로운 접근 방식으로 인간과 유사한 방법인 병렬처리 방식을 구현할 수 있다고 평가되고 있다.

그러므로 이러한 기술혁명의 토대가 될 수 있는 멤리스터 소자 기술이 다양한 인공지능 서비스에 도입될 경우 인간의 뇌와 유사한 인식, 판단, 해석 등이 가능할 것으로 예측된다.

기술의 특성

멤리스터 소자는 전술한 바와 같이 2007년을 기화로 연구가 폭발적으로 증가하고 있다. 특히 2008년 Strukov 등의 연구에 따르면, 금속/절연체/금속의 구조에서 저항이 전류의 이력에 의존하는 것을 확인 하였다. 이와 같은 결과는 S. H. Jo2) 등의 연구 결과에서도 주기적인 인가전압의 증가가 전류의 최고점의 증가로 이어지는 현상으로 확인되었다. 이는 시냅스에서 반복적 자극에 의해 시냅스 신호 증가가 나타나는 현상과 매우 유사한 것으로 판단되었다. 현재까지 주로 개발되고 있는 멤리스터 소자는 2차원 구조를 가지고 있으며 2차원 멤리스터의 가장 큰 특징은 주어진 이전 상황을 기억하기 위한 프로세스 진행 시형성되는 필라멘트에 있다고 알려져 있다. 그러나 아직까지는 이러한 필라멘트의 제어를 위한 직접적인 기술, 즉 위치 및 형성 조건에 대한 연구는 미진한 편이다. 일반적으로 필라멘트의 형성문제를 해결하기 위해 시도되는 방법으로는 주로 나노선을 활용하는 방법이 제시되고 있다. 지금까지 연구되고 있는 멤리 스터 소자는 대체로 2-단자형의 수직 크로스바형태의 구조를 갖고 있지만 트랜지스터를 모사한 3단자 형태의 소자의 제작도 일부 연구되고 있는 것으로 보고된다.3)

멤리스터 소자는 인간 두뇌의 시냅스와 유사성을 갖는다는 점에서 획기적인 기능을 기대할 수 있다. 즉, 인체 신경의 기본적인 구조인 시냅스와 기능적으로 매우 유사한 작용을 함으로써 신경망 소자의 구현이 가능하다. 따라서 이러한 기능은 뉴로모픽 기술로 발전하여 인공지능, 통신, 전자기기 등으로 확산할 것으로 기대된다. 또한 뉴로모픽 소자의 기존 전자소자와 대별되는 기능 중 하나는 다중 레벨 응답 기능 이다. 즉, 현재는 0과 1의 이진법으로 계산하여 정보를 주고받기 때문에 소자의 기능이 매우 단순하며, 이를 구동하기 위한 알고리즘도 저차원 레벨로 구현된다. 그러나 인간의 두뇌와 유사하게 매우 복잡하고 다양한 병렬처리를 위해서는 다중 레벨의 응답 기능이 필수적이다. 따라서 진정한 뉴로모픽 기술을 인공 지능에 적용하기 위한 다중 레벨의 응답을 위해서는 다양한 레벨의 리셋 전압에 대한 연구와 각 리셋 전압에 따른 응답 레벨에 대한 재현성 확보가 매우 중요한 목표가 될 것으로 판단된다.

2) Nanoscalememristor device as synapse in Neuromorphic systems, Nano Lett., vol. 10, 2010, pp. 1297-1301.

3) Q. Xia et al., “Two- and three terminal resistive switches: Nanometer scale memristors and memis tors,” Adv. Funct. Mater., vol. 21, no. 14, July 22th, 2011, pp. 2660-2665.

뉴로모픽용 멤리스터 기술의 개발동향

멤리스터 소자는 아직 성공적으로 산업화에 진입하지 못하고 있다. 뉴로모픽 기술 구현을 위한 중요한 특성 중에서 내구성 및 다중 레벨 응답이 가능한 소자 동작에 대한 재현성이 확보되지 않은 것으로 판단된다.

그러나 최근 들어 인공지능에 대한 산업계의 수요가 폭발적으로 증대되고 있는 상황으로 인하여 안정적인 기능이 가능한 멤리스터 소자에 대한 연구가 학계를 중심으로 활발하게 이루어지고 있다.

2017년 연구진들은 HfZrOx 소재를 기반으로 하여 시냅스 소자의 분극특성을 보고하였으며, SK하이닉스 서울대 연구팀은 Si-doped HfO₂을 이용한 소자의 스위칭 속도 향상에 대한 결과 IEDM (2017)를 발표했다.

벨기에 IMEC은 2017년 Panasonic과 함께 40nm 기술을 이용하여 1T1R 구조의 Ta2O5/ TaOx RRAM 소자를 개발했다고 발표했다. 미국에서는 애리조나 대학이 Ag-GeSe3-Ni을 기반으로 한 Conductive Bridge Random Access Memory(CBRAM)라는 소자를 제안하였다. 이 소자에서 열처리 공정의 최적화를 통해 점진적인 스위칭이 가능한 시냅스 소자를 개발했다고 발표하여 산화물 기반의 멤리스터 소자가 아닌 새로운 소재를 활용한 기술로 주목받았다.

주요 뉴로모픽용 멤리스터 기술의 표준 트렌드

제안된 기술의 산업화를 위해서는 반드시 표준화 과정을 거치게 되어 있다. 이러한 표준개발은 제품의 출시와 함께 사실상 표준이 개발되며, 산업화가 성장기에 이를 때 공적 표준인 국제표준의 제정을 통해 기술적 완성도에 도달하게 된다. 뉴로모픽용 멤리스터 소자 기술의 경우 아직 사실상 표준뿐만 아니라 국제표준의 개발이 요원한 상황이다. 그럼에도 불구하고 멤리스터 기술은 선행표준의 필요성이 증대됨에 따라 사실상 표준보다 국제표준 개발이 먼저 시도되고 있는 상황이다.

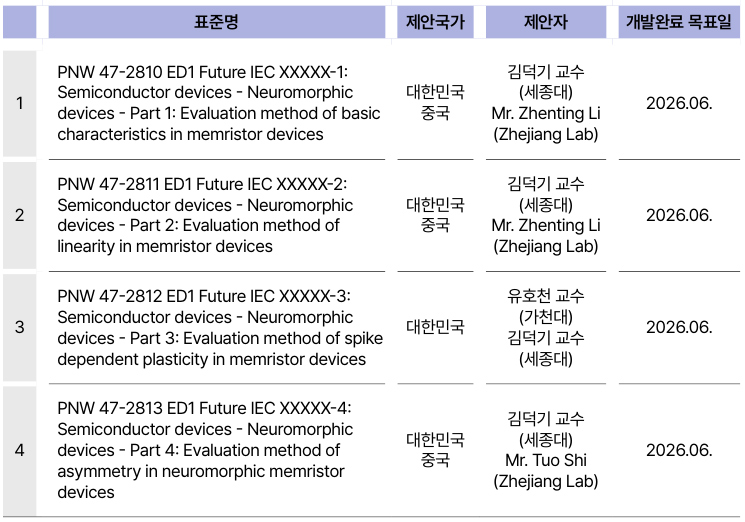

현재 멤리스터 기술 관련 국제표준을 개발하고 있는 기구는 IEC(International Electrotechnical Commission)이다. IEC는 주로 전기·전자 부품에 대한 국제표준을 제정하고 있는 국제표준화기구로써 멤리스터 기술에 대한 표준은 TC 47(Technical Committee: Semiconductor Devices)에서 2022년 정례회의에서 최초로 제안 및 검토되었다.4) 그 후 2023년 Interim 회의에서 제안 내용에 대한 검토가 완료되어 현재 정식 국제표준 개발 프로젝트로 등록되었다. 아래 표에 현재 제안된 뉴로모픽용 멤리스터 기술에 대한 국제표준안에 대한 제목과 제안국가 및 제안자를 나타냈다.

제안된 국제표준 내용

1) PNW 47-2810 ED1 Future IEC XXXXX-1: Semiconductor devices - Neuromorphic devices - Part 1: Evaluation method of basic characteristics in memristor devices

위 표준안은 뉴로모픽용 멤리스터 소자에 있어서 가장 기초적인 특성 평가에 대한 방법을 제시하고 있다.

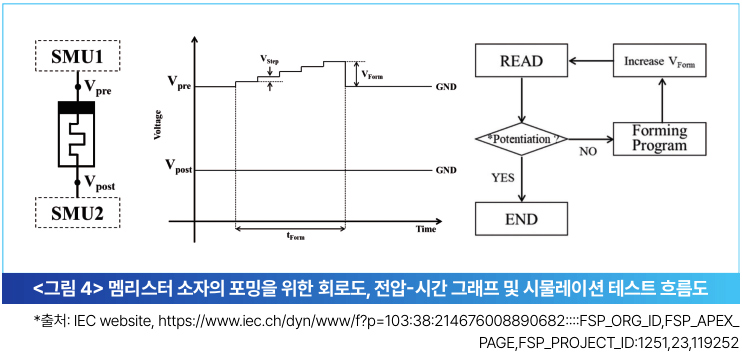

이 표준안은 표준의 범위, 참고표준, 용어를 기술하고 DUT (Device Under Test)와 평가도구 및 환경과 평가방법을 기술하고 있다. 이 표준안에서는 멤리스터 소자의 기록된 정보를 읽는 법, 필라멘트 포밍법, 및 초기화 방법에 대한 회로 구성 및 시뮬레이션 테스트 방법을 제시한다.

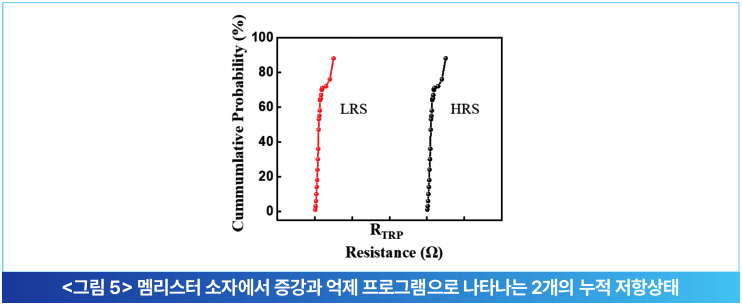

또한 표준안에서는 실험으로 얻어진 멤리스터 소자 2개의 저항상태에 대한 예시를 제시하고 있다. 이러한 시냅틱 특성이 증강(potentiation)과 억제(depression) 프로그래밍을 통해서 나타나고 있음을 보여준다.

2) PNW 47-2811 ED1 Future IEC XXXXX-2: Semiconductor devices - Neuromorphic devices - Part 2: Evaluation method of linearity in memristor devices

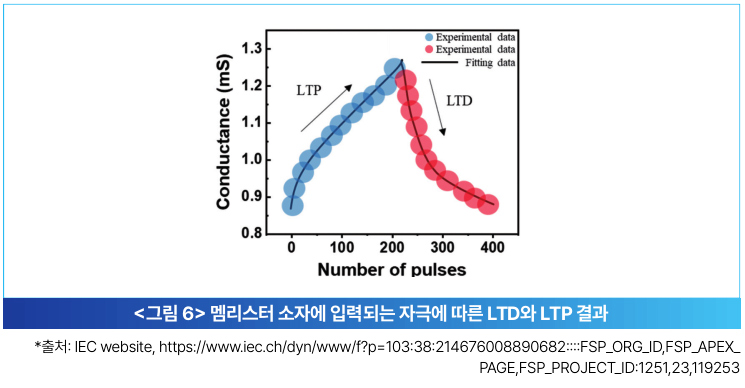

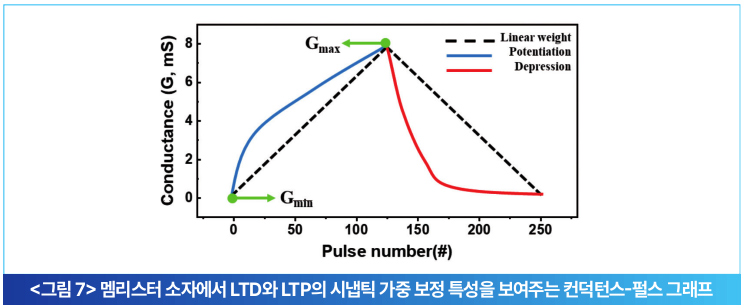

파트2로 제안된 국제표준안은 뉴로모픽용 멤리스터 소자에 있어서 중요한 특성인 장기간 증강(Long Term Potentiation, LTP)과 장기간 억제(Long Term Depression, LTD) 및 선형성의 평가방법을 제시하고 있다. 파트1과 마찬가지로 표준안의 범위와 참고표준, 그리고 본 표준안에서 사용되는 기술용어에 대한 정의를 기술했다. 이어서 LTD, LTP, 및 Linearity의 평가방법을 기술하였으며 추가로 멤리스터 소자의 내구성(endurance)와 보존성(retention)의 이론과 측정법을 상술하였다. <그림 6>은 뉴로모픽용 멤리스터 소자에 입력되는 자극이 있는 경우에 나타나는 LTP와 LTD의 실험적 결과를 제시한다.

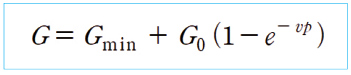

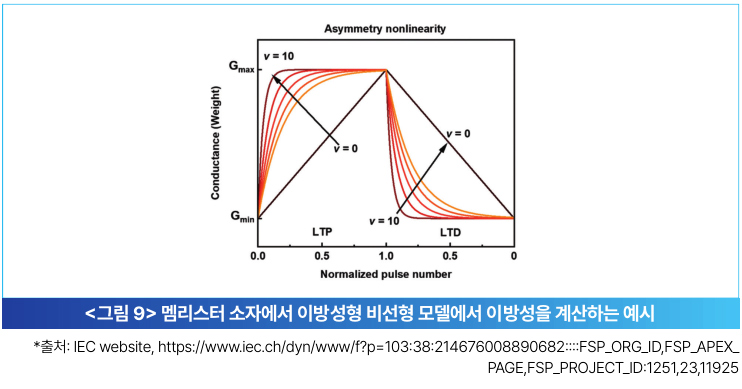

아울러 뉴로모픽용 멤리스터 소자에서 중요한 선형성에 대한 측정방법도 아래와 같이 예시적으로 제시 한다. 이때 선형성 요소는 멤리스터의 증강 연관식에서 계수 v로 정의될 수 있다. 증강 연관식은 다음과 같다.

위의 식에서 Gmin은 최소 컨덕턴스, G0는 참조 컨덕턴스, P는 정규화한 펄스 숫자를 나타낸다. 아래 그림은 선형성 가중치에 대한 LTP 및 LTD의 상관관계를 나타낸 것이다.

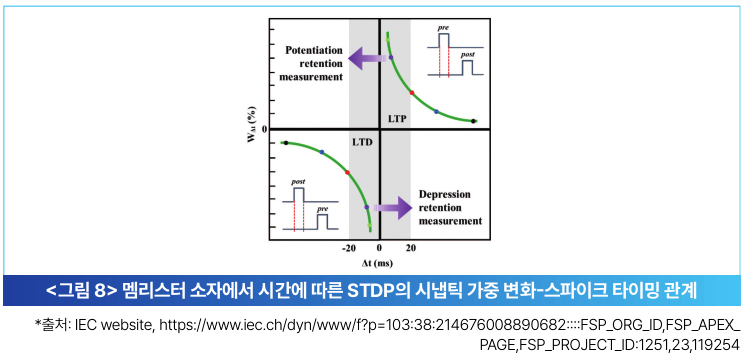

3) PNW 47-2812 ED1 Future IEC XXXXX-3: Semiconductor devices - Neuromorphic devices - Part 3: Evaluation method of spike dependent plasticity in memristor devices

파트3에서는 멤리스터 소자에서 스파이크 의존 가소성의 평가법을 주로 제안하고 있다. 이 표준안에서 검토하고 있는 멤리스터의 특성은 스파이크 시간 의존 가소성(Spike Time Dependent Plasticity, STDP), 간접 STDP, 스파이크 속도 의존 가소성(Spike Rate Dependent Plasticity, SRDP) 및 STDP와 간접 STDP, SRDP의 보존성 특성의 평가법을 취급하고 있다. 파트3 역시 파트 1,2와 마찬가지로 제안한 표준의 범위, 참고문헌, 본 제안 표준에서 사용하는 기술용어의 정의를 우선적으로 기술하고 있다. 이어서 표준안에서는 STDP, 간접 STDP, SRDP 및 보존성을 측정하는 방법을 제시하고 있다.

4) PNW 47-2813 ED1 Future IEC XXXXX-4: Semiconductor devices - Neuromorphic devices - Part 4: Evaluation method of asymmetry in neuromorphic memristor devices

시리즈 표준안의 마지막 표준인 파트4는 뉴로모픽용 멤리스터 소자의 이방성 측정법을 제시한다. 본표준안도 시리즈 표준과 마찬가지로 본 제안 표준의 범위, 참고문헌 및 기술용어의 정의로 표준안을 시작 한다. 멤리스터 소자에서 이방성의 측정방법과 이방성이 있는 비선형 모델로부터 이방성을 계산하는 방법을 제시한다. <그림 8>은 이방성형 비선형 모델에서 이방성을 측정하는 방법에 대한 그래프를 나타낸 것이다. 본 표준안에서는 등방성형 비선형 모델에서도 이방성을 계산하는 방법도 제시한다.

멤리스터 기술 표준의 개발방향

본 기술은 아직까지 제품화 및 이를 기반으로 하는 표준안 개발이 완료되지 않았다. 현재 개발중인 표준은 제안 단계로 기술적으로 국가 간 합의를 통한 개발이 더욱 요구된다. 향후 뉴로모픽용 멤리스터 기술의 표준화 방향은 현재 기술개발 수준 및 속도를 감안할 경우 3가지의 표준개발 방향이 가능할 것으로 보인다.

1) 다중 레벨 구현

멤리스터 소자의 가장 큰 기대점은 인공지능에서의 활용성이다. 따라서 기존의 소자들을 이용하여 구현 하기 어려운 병렬처리에 대한 알고리즘을 구현하는 것이 매우 중요하다. 이러한 응용에 있어서 멤리스터 소자를 활용할 경우 다중 레벨의 응답이 가능한 것으로 보고된다. 그러므로 향후 표준기술의 개발은 다중 레벨과 관련된 아이템의 발굴이 필요할 것으로 생각된다. 특히 다중 레벨 응답이 가능하기 위해서는 재현 성의 확보가 매우 중요한 요소가 된다. 표준개발은 이 분야에서 우선하여 개발될 것이라고 예상할 수 있다.

2) 멤리스터 소자의 내구성

기존 전자소자의 경우 오랜 기간 소재 연구와 공정의 개발을 통하여 안정된 소자구조를 확립하였으며, 이를 바탕으로 균일한 특성의 구동을 확보하고 있다. 그러나 멤리스터 소자의 경우 현재 주로 소재는 TiO2또는 Ta2O5 등의 금속계 산화물을 이용하고 있기 때문에 공정 및 재료에 따라서 균일한 특성을 얻기가 어렵다.

따라서 금속계 산화물 공정 시 매우 균일한 매트릭스 형성을 위한 공정조건에 대한 선행연구가 필요한 것으로 판단된다. 멤리스터 소자의 경우 이를 전자소자에 사용하기 위해서는 적어도 1010회 수준의 내구성이 확보되어야 한다. 따라서 이러한 내구성 평가에 대한 표준도 개발이 필요한 항목이라고 판단된다.

3) 3D 다층 집적화 기술

전자소자에 있어서 최근 관심은 선폭의 축소를 통한 저전력, 고집적도의 달성으로 발전하고 있다. 따라서 멤리스터 소자 역시 집적화의 요구를 수용하는 방향으로 개발할 필요가 있다. 이 경우 요구되는 집적도는 1시냅스 소자의 면적을 ~10nm2 수준 이하로 제어하여야 한다. 이 경우 스위칭시에 소비되는 전력도 대략 10fJ 이하로 설정할 수 있을 것으로 기대된다. 위의 조건들을 모두 만족할 경우에도 향후에 더 높은 집적도를 요청할 것으로 예측되고 있다. 그러므로 이러한 요구사항을 만족하기 위해서는 3D 다층 집적화 기술을 통한 획기적인 집적도 향상 기술은 필수적으로 개발하여야 한다. 이 경우 기존 메모리 소자에서 개발된 256층을 쌓는 낸드 플래시 메모리 개발과 병행하지만 뉴로모픽용 멤리스터만의 고유한 공정이 채용된 3D 표준기술의 개발이 필요할 것으로 생각된다.